# Creating safety. With passion.

The SafeFlex — Functional Safety Development Kit (FSDK) consists of an FPGA based evaluation board. With the realization of an FPGA based solution in safety related systems, a considerable reduction in costs for development and certification is achieved. Time to market is reduced noticeably.

The SAFEFLEX – FSDK includes an instruction manual for the whole safety development and assists you to reduce risks, design costs, design time, process overhead. It improves your platform development, flexibility, modularity and safety integrity level (SIL).

# **Concept proved by TÜV Rheinland:**

The SafeFlex — FSDK demontrates examples of typical applications together with documentation and process steps, which are needed to fulfil all the requirements of the following safety standards:

IEC 61508 standard up to SIL 3 ISO 13849 standard up to PI e Cat. 4

# **Typical applications**

Industrial Automotive Energy Management etc.

#### **Support**

You can use the SAFEFLEX – FSDK as your own safety development platform to design and realize systems for instance of:

Safe system shutdown; Signal processing with high data volume; Image data processing;

## openSAFETY Solution

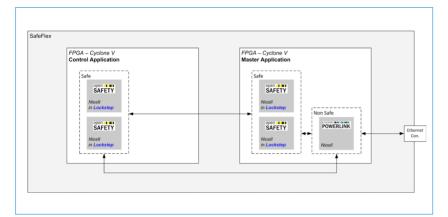

The concept is discussed with the TÜV Rheinland for safety systems up to IEC 61508 - SIL3 and is depicted in following block diagram. SAFEFLEX — FSDK is supporting now fieldbus communication with a safety protocol. The first supported fieldbus is the Ethernet POWERLINK from our partners EPSG and Softing. openSAFETY from EPSG is used as safety protocol.

The application for the SAFEFLEX board will be downloadable from www.safeflex-fsdk.com.

The architecture describes a system consisting of two FPGAs. Each FPGA design consisting of two softcore processors with openSAFETY stack in lockstep. One of the FPGAS has an additional processor with a POWERLINK stack.

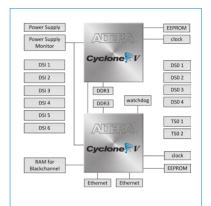

#### **Technical Data**

| Operating Voltage                                          |

|------------------------------------------------------------|

| FPGA Main                                                  |

| FPGA Child                                                 |

| DDR3 SDRAM 2-Gbit(128Mbx32)(two devices per FPGA)          |

| EEPROM                                                     |

| Clock Speed                                                |

| DSI Signal 0                                               |

| DSI Signal 1                                               |

| DSO continuous current500mA                                |

| DSO short circuit protection external protection necessary |

| DSO switching frequency                                    |

| Networking                                                 |

| Standard Digital I/O Pins (3.3V)                           |

| Support Arduino Shields                                    |

| Length                                                     |

| Width                                                      |

## **Key Features**

1oo2 architecture

HFT = 1 (IEC 61508)

Two FPGA

6 safety digital signal inputs

4 safety digital signal outputs

2 test outputs

DDR3 SDRAM

**EEPROM**

watchdog

2 Industrial Ethernet

monitored power supply